FPGA中的竞争与冒险

2018-06-25 16:46:52

作者:电气事业部 邬若愚 指导:电气事业部 杜万金

FPGA(Field-Programmable Gate Array)即现场可编程门阵列,在结构上由逻辑功能块排列为阵列,并且由可编程的内部连线来连接这些功能块来实现一定的逻辑功能。

信号在传输和处理过程中,通过FPGA内部的连线和逻辑单元时,都有一定的延时。延时的大小和连线的长短,逻辑单元的数目有关,同时也受到器件的制造工艺、工作电压、温度等条件的影响,信号的电平转换也需要一定的过渡时间。造成信号的原变量和反变量状态改变的时刻不一致,这种现象称为竞争。

由于竞争而引起电路输出信号中出现了非预期信号,产生瞬间错误的现象称为冒险。表现为输出端出现了原设计中没有的窄脉冲,常称为毛刺。

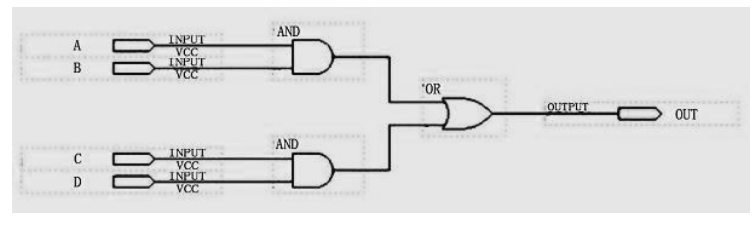

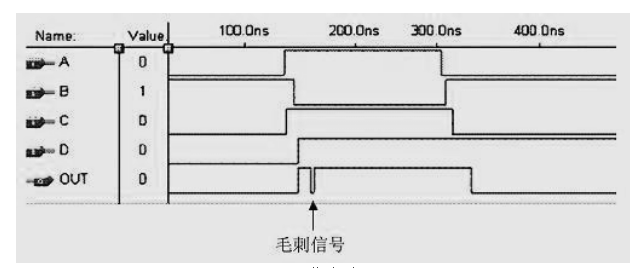

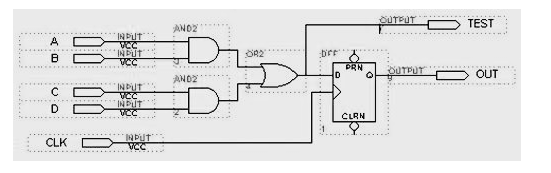

图1 逻辑冒险

即使是在最简单的逻辑运算中,如果出现多路信号同时跳变的情况,在通过内部走线以后,也一定会产生毛刺。如上图所示,A、B、C、D四个输入信号经过布线延时后,高低电平变换不是同时发生的,这导致输出信号出现了毛刺。

和分立元件不同,FPGA内部不存在寄生电容和电感,所以无法过滤电路中的毛刺,从而使得毛刺将被完整保留下来,并且逐级传递,对电路的影响更加突出。冒险往往会影响到逻辑电路的稳定性,而时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都有可能导致系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。

可以利用冗余项来消除毛刺,函数式和真值表所描述的是静态逻辑,而竞争则是从一种稳态到另一种稳态的过程。因此竞争是动态过程,它发生在输入变量变化时。此时,修改卡诺图,增加多余项,在卡诺图的两圆相切处增加一个圆,可以消除逻辑冒险。

也可以通过改变设计,破坏毛刺产生的条件来完成。由于格雷码计数器的输出每次都只有一位的跳变,消除了竞争冒险的条件,所以在数字电路的设计过程中往往采用格雷码计数器来代替普通的二进制计数器来避免毛刺的产生。

毛刺并不是对所有输入都有危害,例如D触发器的输入端,只要毛刺不出现在时钟的上升沿并且满足一定时间,就不会对系统造成危害,也就是说D触发器的D输入端对毛刺不敏感。根据这个特性我们应该在系统中尽可能的采用同步时钟,由于毛刺持续时间很短,一般不会满足数据的建立和保存时间,从而降低毛刺对系统的危害。

但是以上方法并不能完全消除毛刺,所以我们需要采取“采样”的方法。一般冒险都出现在信号发生电平转换的时刻,也就是说毛刺是在输出信号产生的时候出现的,而在输出信号保持的期间不会有毛刺产生,所以我们可以通过在输出信号保持期间对其进行采样,从而消除毛刺的影响。

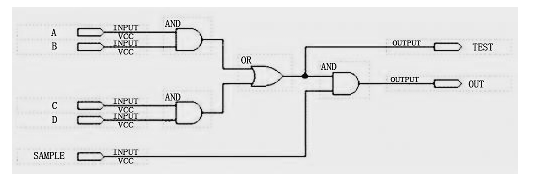

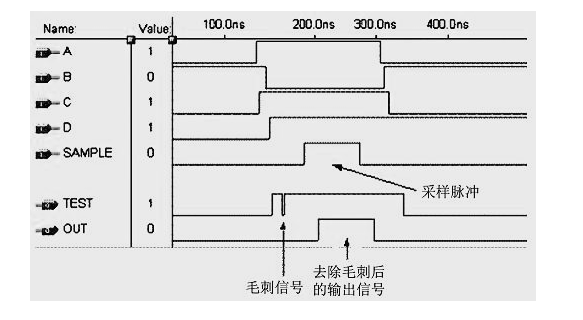

有两种基本采样方法,一种是在输出信号保持期间,用一定宽度的高电平脉冲与输出信号做逻辑“与”运算,由此采样得到输出信号的电平值。如图二所示,加入“SAMPLE”采样信号,从而消除毛刺影响。这种方法的缺点是必须人为的保证SAMPLE信号必须在合适的时间中产生。

图2 采样方法一

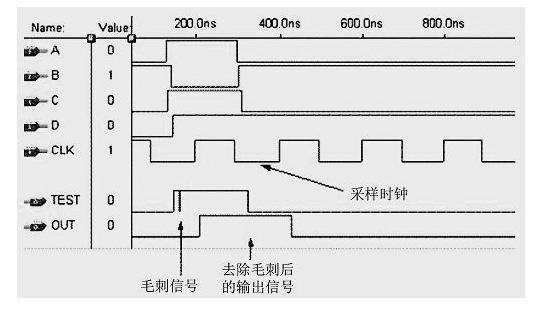

另一种更常见的方法是利用之前提到的D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。如图三所示,在电路中增加了采样时钟和D触发器,在时钟上升沿时进行采样从而减少毛刺的影响。

图3 采样方法二

除此以外消除毛刺还有吸收法和延迟法等。其中吸收法是通过增加输出滤波完成,但是会破坏输出波形,因此该方法不宜在中间级使用。延迟法是通过找到产生延迟的支路,加上毛刺宽度的延迟来消除毛刺。

在FPGA设计的时候就应该考虑到毛刺的影响,因此需要注意以下几点:采用寄存器和触发器来设计电路,尽量不选用锁存器,因为锁存器对毛刺十分敏感;尽量避免隐含RS触发器的出现,一般要控制输出被直接反馈到输入端,采用反馈环路会出现隐含RS触发器,其对输入尖峰和假信号很敏感,输入端有任何变化都有可能使输出值立刻改变,此时易造成毛刺的产生,导致时序的严重混乱;注意译码逻辑电路,因为译码器和比较器本身会产生尖峰,容易产生毛刺,如果把译码器或比较器的输出直接连到时钟输入端或异步清除端,会造成严重的后果;每一个模块中只用一个时钟,避免使用多时钟设计,对所有模块的输入时钟、输入信号、输出信号都用D触发器或寄存器进行同步处理,即输出信号直接来自触发器或寄存器的输出端。

毛刺是FPGA设计中不可忽视的问题,只有在设计时就注意避免产生毛刺,后期做好消除毛刺的工作,才能够解决FPGA竞争冒险的问题,从而增强电路的稳定性和可靠性,并为实际电路的测试带来方便。